CS230/EIE230 Computer Organization

HomeWork

计算机组织代写 Suppose the following code snippet will run on the RV32I pipelined processor introduced on slide 80 of Lecture 6.

(5 Points) Suppose the following code snippet will run on the RV32I pipelined processor introduced on slide 80 of Lecture 6.

beq x3, x4, L1

addi x5, x5, -4

L1: lw x3, 0(x5)

andi x3, x3, 0xff

add x4, x3, x4

sw x4, 0(x5)

We make the following assumptions: 计算机组织代写

- Each register contains a value which is equal to its register address x 4. For instance, register x8 contains 32, register x29 contains 116, and so forth

- All data memory locations contain a constant value 99

- Prior instructions are sequential instructions

2) Please fill in the following table to describe the pipelined execution in multi-cycle view until the last instruction completes execution. Note, each cell should be one of the three cases:

a.the instruction number that is in that pipeline stage

b.NOP to indicate a pipeline bubble

c.Empty cell to indicate an earlier or later instruction that is outside the scope of the code snippet.

| Cycle | IF | ID | EX | MEM | WB |

| 1 | 1 | ||||

| 2 | 1 | ||||

| 3 | 1 | ||||

| 4 | 1 | ||||

| 5 | 1 | ||||

| 6 | |||||

| 7 | |||||

| 8 | |||||

| 9 | |||||

| 10 | |||||

| 11 | |||||

| 12 | |||||

| 13 | |||||

| 14 | |||||

| 15 | |||||

2) Please fill in the following table on all changes to either a register or a memory location, and give its old value and new value at the same time. For example, if the lw instruction updates register x3 from old value 12 to new value 99 at clock cycle 5, then the 5thentry of the table will be look like this: 计算机组织代写

| Cycle | Register# | Mem Address | Old Value | New Value |

| 5 | 3 | 12 | 99 |

| Cycle | Register# | Mem Address | Old Value | New Value |

- (5 Points) Suppose a computer has a memory hierarchy consisting of virtual memory and cache with configurations described in the following table.

| Addressing | Virtual address: 14-bit |

| Physical address: 12-bit | |

| Page size: 64 bytes | |

| TLB | 16 entries |

| 4-way set associative | |

| Cache | 16 cache blocks |

| 4-byte block size | |

| Direct-mapped |

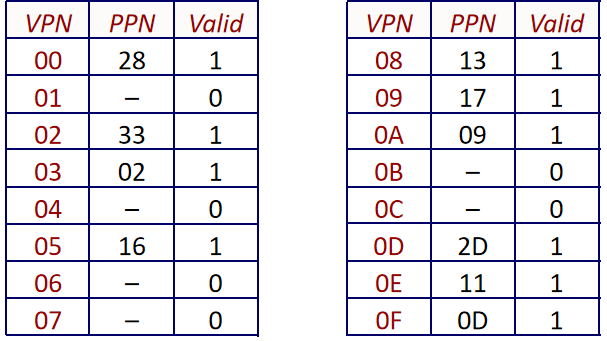

The partial page table (showing only the first 16 PTE entries (out of 256) are given below:

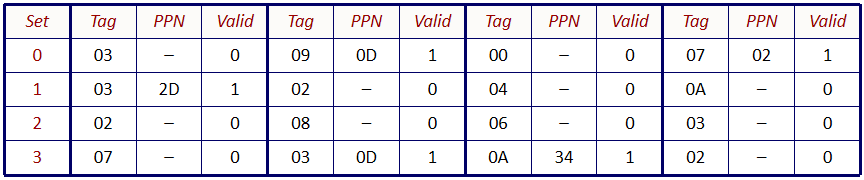

The TLB has the following content:

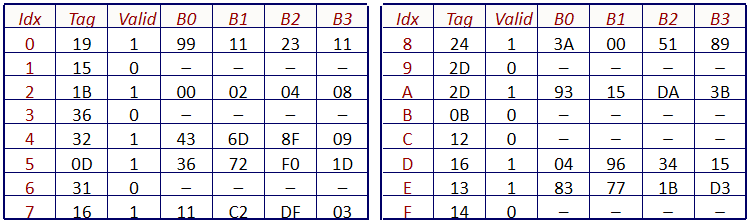

The cache has the following content:

-

Please gives the size (bits) of the following fields (e.g., the VPO is 6-bit) 计算机组织代写

| Field | Description | Size |

| VPN | Virtual Page Number | |

| VPO | Virtual Page Offset | 6 |

| PPN | Physical Page Number | |

| PPO | Physical Page Offset | |

| TLBT | TLB Tag | |

| TLBI | TLB Index | |

| CT | Cache Tag | |

| CI | Cache Index | |

| CO | Cache Block Offset |

2) Please fill in the various information (numbers should be hexadecimal) for the following two virtual addresses

| Field | VA: 0x03D4 | VA: 0x0020 |

| VPN | ||

| VPO | ||

| PPN | ||

| PPO | ||

| TLBT | ||

| TLBI | ||

| CT | ||

| CI | ||

| CO | ||

| TLB Hit/Miss | ||

| Page Hit/Miss | ||

| Cache Hit/Miss | ||

| Data (applicable only for cache hit) |